# A LOW-POWER X-BAND FREQUENCY SYNTHESIZER MODULE

Tadao Nakagawa, Hiroshi Okazaki, and Yo Yamaguchi

NTT Wireless Systems Laboratories

1-1 Hikarinooka, Yokosuka-shi, Kanagawa 239, Japan

## ABSTRACT

This paper describes an X-band frequency synthesizer that features low power consumption. To save power and reduce cost, new MMIC's were developed and combined with commercially available components. With +10 dBm output, the power consumption is 270 mW, the lowest ever reported for X-band synthesizers.

## INTRODUCTION

There is a growing demand for wireless communications at high data rates for multimedia services [1]. High data rates require more bandwidth and hence higher carrier frequency. Currently, wireless local area network (LAN) systems providing 10 Mbit/s in the 19-GHz band are available in Japan, and other systems with high data rates are being investigated worldwide [2], [3]. The next generation of wireless LAN's will use portable terminals and service coverage will be expanded to the outdoors [4], [5]. Because these terminals will be battery operated, power consumption must be minimized. Further reductions of power consumption have been difficult due to the use of local oscillators that consist of many analog and digital circuits. The power consumption of local oscillators, including fixed frequency oscillators, beyond the C-band is more than 1 W [6]-[13].

This paper presents an X-band frequency synthesizer whose power consumption is only 270 mW with +10 dBm output. To achieve the low power consumption and reduce cost, we developed new MMIC's and combined them with commercially available devices. All the elements are fabricated on a board.

## SYNTHESIZER MODULE DESIGN

Our target frequency for the local oscillator is 9.6 GHz. The oscillator is combined with a harmonic mixer for 19 GHz frequency conversion. There are several configurations with which 9.6 GHz output can be obtained, among them 9.6 GHz direct oscillation and 9.6/n GHz oscillation with times-n multiplication, where n is an integer. Direct oscillation at 9.6 GHz can be effortlessly obtained with a mature GaAs MESFET process; however, frequency dividers following a voltage-controlled oscillator (VCO) have more than 400 mW dissipation [14], [15]. On the other hand, larger n results in spurious signal increase around the carrier.

A configuration with 2.4-GHz oscillation and times-4 multiplication was selected to meet power, cost and performance requirements. In the 2.4-GHz band, devices using a 3 V supply are commercially available for the VCO and the phase-locked loop (PLL) IC. Many types of VCO's have been developed with the ongoing development of new types of MMIC's; however, they typically have rather high phase noise. A hybrid configuration for the VCO may well be an effective means of addressing this problem. The multipliers and amplifiers, in contrast, are MMIC's designed for low-power performance.

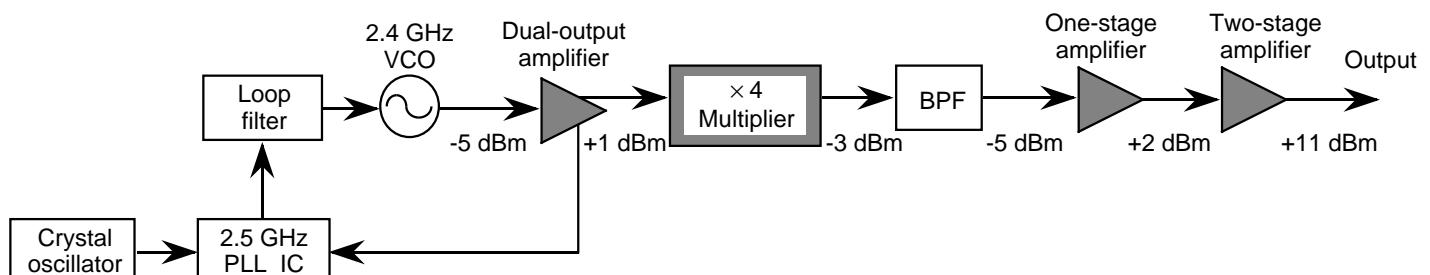

Figure 1 shows a block diagram of the X-band frequency synthesizer along with its level diagram. Level design affects power consumption directly. Saturation output power is proportional to DC power dissipation. Accordingly, all signal levels except that at the final stage are set low, or in other words, the allowable current dissipation is low. Final output power meets the system requirement, which is more than +8 dBm.

Figure 1: Module configuration and its level diagram.

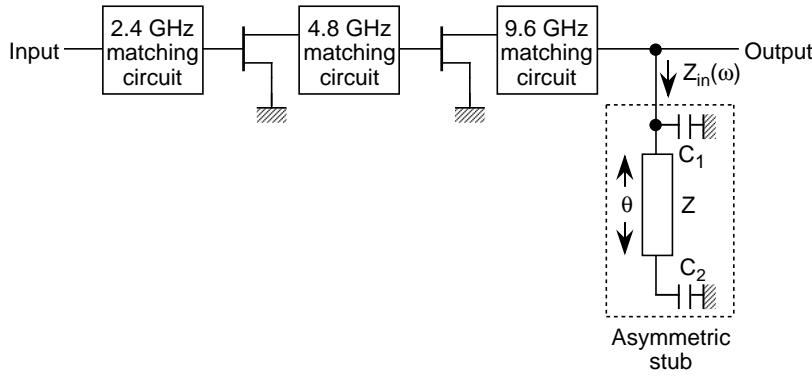

Figure 2: Frequency quadrupler with an asymmetric stub.

## MMIC DESIGN AND PERFORMANCE

### Multiplier

Commercially available microwave frequency doublers are usually diode type, thus their DC power dissipation is 0. However, their conversion loss is generally more than 10 dB, and hence more than 20 dB for frequency quadruplers, i.e., two-stage doublers. Moreover, the required input power is more than +10 dBm. The power consumption of amplifiers for driving the frequency doubler and compensating conversion loss is therefore large.

FET multipliers biased in the nonlinear operation region have low conversion loss and low input power [16]. However, they pose a problem for fundamental frequency suppression. Though a balanced configuration is attractive for fundamental frequency suppression [17], this type of FET multiplier dissipates twice as much power as a single FET multiplier. A single-ended FET multiplier combined with a quarter wavelength stub can suppress the fundamental frequency component. However, the stub is quite large at the 4.8 GHz band, i.e., 6.3 mm on a GaAs substrate. This results in high chip cost. A quarter-wavelength transmission line can be shortened by combining a high impedance transmission line with shunt capacitors [18]. Unfortunately, the open frequency of the shortened transmission line is not a harmonic of the short frequency, thus it is not suitable for the stub of the multipliers.

We devised an asymmetric stub and applied the single-ended FET multiplier shown in Fig. 2. Capacitors  $C_1$  and  $C_2$  are

$$C_1 = \frac{1}{\omega_0 Z \tan \theta} \quad (1)$$

$$C_2 = \frac{C_1 \cos^2 \theta}{2 \cos^2 \theta + 1} \quad (2)$$

where  $\omega_0$ ,  $Z$ ,  $\theta$  are the fundamental angular frequency, the characteristic impedance of the stub, and the electrical angle of the stub, respectively. When frequency  $\omega$  is equal to  $\omega_0$ , the

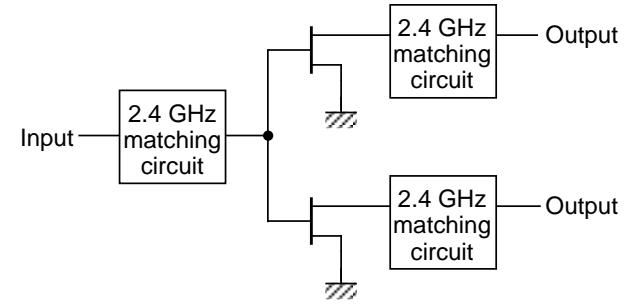

Figure 3: Dual-output amplifier.

input impedance of the stub,  $Z_{in}(\omega)$ , is 0. When  $\omega$  is equal to  $2\omega_0$ ,  $Z_{in}(\omega)$  is  $\infty$ .

This stub was fabricated by using equivalent lumped elements and applied to a 2.4 to 9.6 GHz frequency quadrupler MMIC with single-ended configuration, where the fundamental frequency of the stub,  $f_0$ , is 4.8 GHz. The resulting GaAs chip area is  $1.5 \text{ mm} \times 1.5 \text{ mm}$ . The 2.4-GHz frequency component is suppressed at the 9.6 GHz matching circuit. Matching circuits were determined on the basis of a harmonic-balance analysis to obtain low conversion loss when input power is 0 dBm. Measured conversion loss is 4.2 dB and the power consumption is 39 mW ( $3 \text{ V} \cdot 13 \text{ mA}$ ) with 2.4 GHz-0 dBm input.

### Dual-output amplifier

The VCO output should be split in two with isolation to prevent the noise of the PLL digital circuit from mixing with the RF signal. Hybrid couplers such as the Wilkinson divider do not have the isolation out of their bandwidth and the circuit is large. A resistive power splitter combined with an attenuator is attractive; however, the amplifiers use a lot of power in compensating for resistive loss. We adopted the dual-output amplifier shown in Fig. 3 to achieve wideband isolation and reduce power and chip area. The gates of two FET's are connected and follow the input matching circuit. Output signals have isolation owing to the reverse transmission coefficient,  $S_{12}$ , of the FET.

The dual-output amplifier is integrated on a  $1.5 \text{ mm} \times 1.5 \text{ mm}$  GaAs chip. Measured gain is 6.3 dB and isolation between the two outputs is 22 dB at 2.4 GHz. The power consumption is 54 mW ( $3 \text{ V} \cdot 18 \text{ mA}$ ).

### X-band amplifier

The one-stage amplifier consists of  $100 \mu\text{m}$  FET and is integrated on a  $1.5 \text{ mm} \times 1.5 \text{ mm}$  GaAs chip. Measured gain is 8.0 dB at 9.6 GHz. The power consumption is 30 mW ( $3 \text{ V} \cdot 10 \text{ mA}$ ).

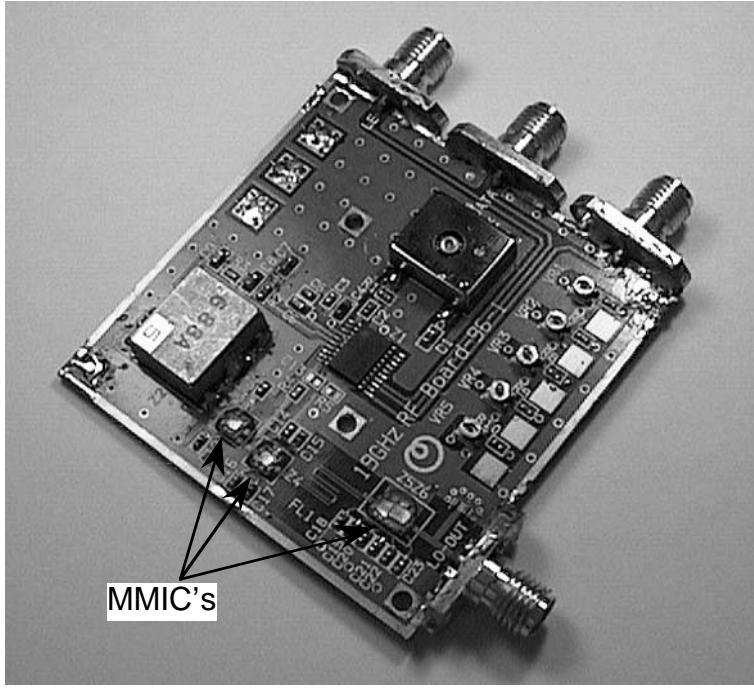

Figure 4: Frequency synthesizer module.

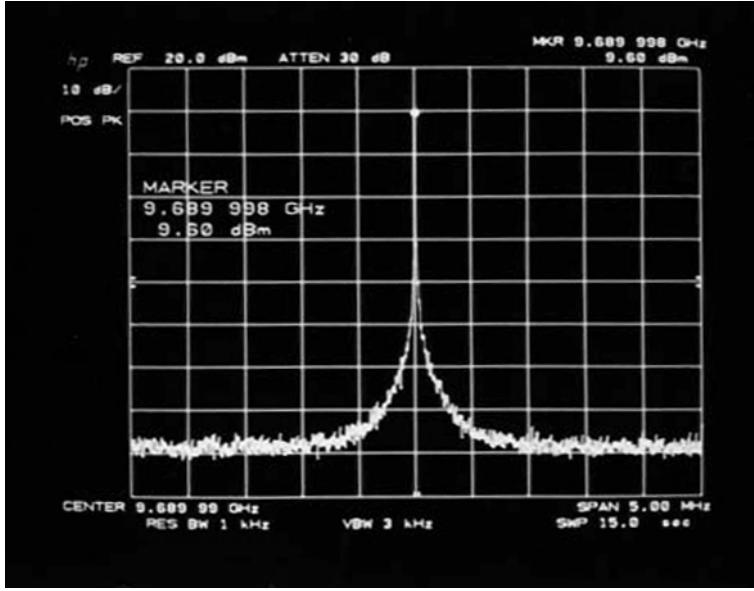

Figure 5: Synthesizer module output spectrum.

H: 500 kHz/div; V: 10 dB/div; R: 1 kHz.

The two-stage amplifier consists of a  $100\text{ }\mu\text{m}$  FET for the first stage and a  $200\text{ }\mu\text{m}$  FET for the second stage. It is integrated on a  $2.0\text{ mm} \times 1.5\text{ mm}$  GaAs chip. Measured gain is 14.3 dB at 9.6 GHz. The power consumption is 90 mW ( $3\text{ V} \cdot 30\text{ mA}$ ).

### SYNTHESIZER MODULE PERFORMANCE

All the circuits are implemented on a board as shown in Fig. 4, where MMIC bare chips are mounted on the board and coated with silicone rubber. The module is  $50\text{ mm} \times 50\text{ mm} \times 6\text{ mm}$  and the weight, excluding the connectors, is 8 g. The board material is BT resin [19]. The loss tangent,  $\tan\delta$ , of the BT resin in the module is 0.0038 and its relative dielectric constant,  $\epsilon_r$ , is 3.3 at 10 GHz.

A bandpass filter follows the frequency quadrupler and it

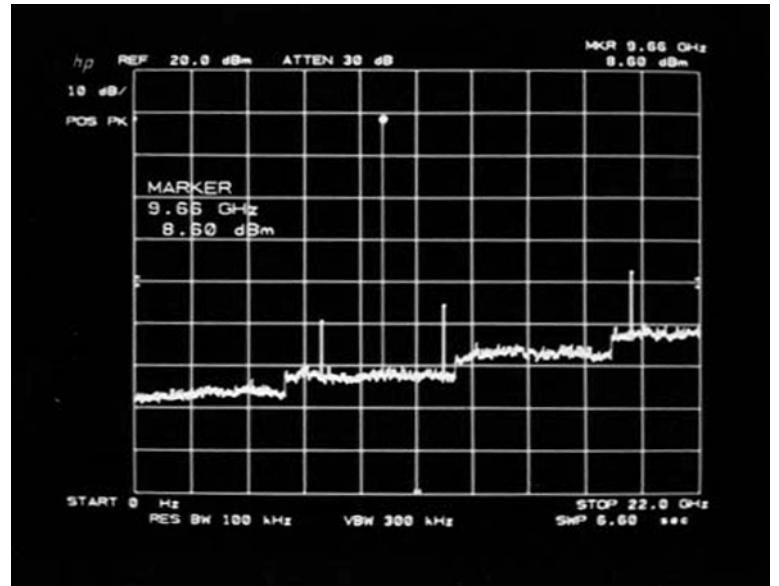

Figure 6: Wide span spectrum.

H: DC-22 GHz; V: 10 dB/div; R: 100 kHz.

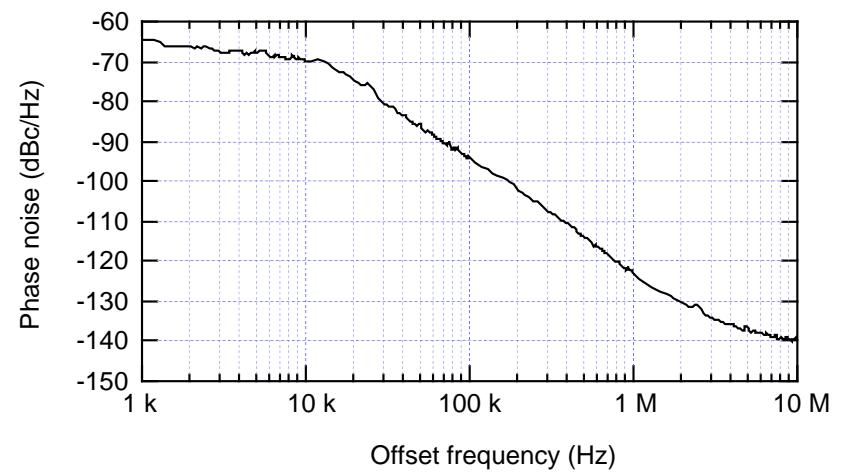

Figure 7: Phase noise performance.

was formed on the board with cascaded coupled lines. It has a measured insertion loss of 1.7 dB at 9.6 GHz, 23.3 dB at 9.6-2.4 = 7.2 GHz, 26.2 dB at 9.6+2.4 = 12 GHz.

Output spectrum is shown in Fig. 5. Loss of the cable used in the measurement was 0.55 dB. The output power of the module is therefore +10.15 dBm. Figure 6 is the DC-22 GHz span spectrum. Spurious levels at the nearest carrier,  $9.6 \pm 2.4$  GHz, are at least 43 dB below the carrier. Phase noise performance is shown in Fig. 7 when the frequency step size is 10 MHz at 9.7 GHz. Phase noise at 1-MHz offset from the carrier is -123 dBc/Hz.

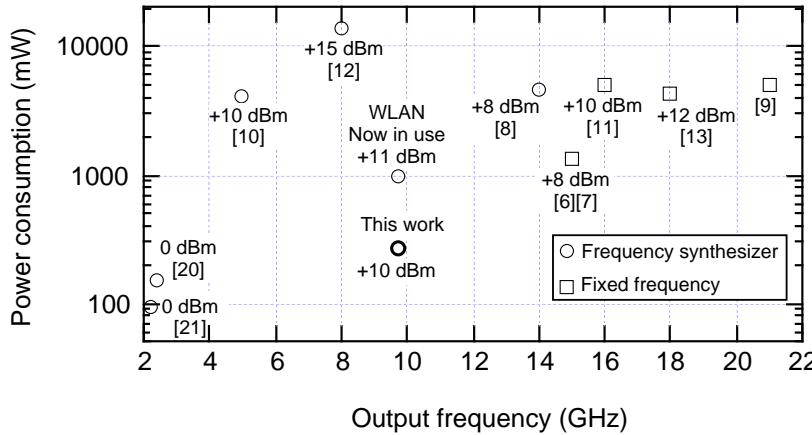

The current dissipations of the VCO, the PLL IC, and the crystal oscillator used in the synthesizer module are 6.5, 11, and 1.5 mA under +3 V supply. The total power consumption of the frequency synthesizer module is 270 mW ( $3\text{ V} \cdot 90\text{ mA}$ ). The power consumption, the output frequency, and the output power (dBm) of the PLL oscillators are compared in Fig. 8. To the author's knowledge, this power consumption is the lowest ever

Figure 8: PLL oscillator comparison.

reported for X-band frequency synthesizers with +10 dBm output.

## CONCLUSION

A new X-band frequency synthesizer module has been developed that features low power consumption. To achieve the low power consumption and reduce cost, MMIC's of a frequency quadrupler with an asymmetric stub, a dual-output amplifier, and X-band amplifiers were newly developed after the module configuration selection and level diagram design, and were combined with a commercially available VCO, PLL IC, and crystal oscillator. The total power consumption of the frequency synthesizer module is 270 mW with +10 dBm output, which is the lowest ever reported for X-band frequency synthesizers. This module can be applied to wireless personal communications with high data rates.

## ACKNOWLEDGMENT

The authors would like to thank Dr. M. Muraguchi and M. Nakatsugawa for their helpful discussions, F. Saito for assistance in module assembly. They also wish to thank A. Hashimoto for his advice and encouragement.

## REFERENCES

- [1] R. Prasad, "Research challenges in future wireless personal communications: microwave perspectives," in 25th European Microwave Conference Proc., Sept. 1995, pp. 4-11.

- [2] H. H. Meinel, "Recent advances on millimeterwave PCN system development in Europe," in 1995 IEEE MTT-S Dig., May 1995, pp. 401-404.

- [3] T. Okada, T. Shirato, H. Hara, and M. Iki, "VJ25 system: 19-GHz high-speed wireless LAN system," NTT Review, vol. 9, no. 1, pp. 86-92, Jan. 1997.

- [4] K. Kohiyama and A. Hashimoto, "Advanced wireless access system," in Telecom 95, Technology Summit, vol. 2, Oct. 1995, pp. 341-345.

- [5] J. S. Dasilva, B. Arroyo, B. Barani, and D. Ikonomou, "European third-

generation mobile systems," IEEE Commun. Mag., vol. 34, no. 10, pp. 68-83, Oct. 1996.

- [6] T. Ohira, H. Kato, K. Araki, and F. Ishitsuka, "A compact full MMIC module for Ku-band phase-locked oscillators," IEEE Trans. Microwave Theory Tech., vol. 37, no. 4, pp. 723-728, Apr. 1989.

- [7] N. Ishihara, H. Ichino, H. Kikuchi, and H. Kato, "IF band amplifier ICs and frequency divider/PFC IC for satellite transponders," NTT Review, vol. 2, no. 2, pp. 116-122, March 1990.

- [8] T. Ohira, M. Muraguchi, T. Hirota, T. Nakagawa, H. Ichino, and M. Togashi, "Ku-band MMIC miniaturized PLL frequency synthesizer," in 1990 Autumn national convention record, the Institute of Electronics, Information and Communication Engineers, Oct. 1990, p. 2-369.

- [9] J. Pérez, P. Dorta, and F. Sierra, "A comparison of the performance of three different phase locked oscillators fabricated at 21 GHz," in 1992 IEEE MTT-S Dig., June 1992, pp. 305-308.

- [10] Sciteq Electronics, Inc., VDS-6030.

- [11] Miteq, Inc., PLO-3000B series.

- [12] Communication Techniques, Inc., Series LCS.

- [13] Communication Techniques, Inc., Series PDRO.

- [14] M. Takahashki, H. Itoh, K. Ueda, and R. Yamamoto, "A 9.5 GHz commercially available 1/4 GaAs dynamic prescaler with suppressed noise performance," in IEEE 1988 Microwave and Millimeter-Wave Monolithic Circuits Symp. Dig., May 1988, pp. 31-35.

- [15] N. H. Sheng, R. L. Pierson, K. C. Wang, R. B. Nubling, P. M. Asbeck, M. F. Chang, W. L. Edwards, R. J. Erlandson, and D. E. Philips, "A high speed multi-modulus HBT prescaler," in IEEE 1990 GaAs IC Symp. Tech. Dig., Oct. 1990, pp. 37-39.

- [16] S. A. Maas, Nonlinear Microwave Circuits. Boston, MA: Artech House, Inc., 1988, pp. 397-416.

- [17] T. Hirota and H. Ogawa, "Uniplaner monolithic frequency doublers," IEEE Trans. Microwave Theory Tech., vol. 37, no. 8, pp. 1249-1254, Aug. 1989.

- [18] T. Hirota, A. Minakawa and M. Muraguchi, "Reduced-size branch-line and rat-race hybrids for uniplanar MMIC's," IEEE Trans. Microwave Theory Tech., vol. 38, no. 3, pp. 270-275, Mar. 1990.

- [19] M. Gaku, N. Ikeguchi, S. Ayano, "BT resin widens the choice of laminate materials," Electronic Packaging & Production, vol. 25, no. 12, pp. 30-33, Dec. 1985.

- [20] VARI-L Company, Inc., PLL300-2450.

- [21] Z-Communications, Inc., Application note AN-106.